US009722705B2

## (12) United States Patent Blumenthal et al.

## Diumenmai et ai.

(54) METHOD AND APPARATUS FOR CONTROLLING, MONITORING, AND COMMUNICATING WITH TUNABLE OPTICAL DEVICES AND SUBASSEMBLIES

(71) Applicant: **OE SOLUTIONS AMERICA, INC.,** Englewood Cliffs, NJ (US)

(72) Inventors: Daniel J. Blumenthal, Englewood Cliffs, NJ (US); Holger Klein, Englewood Cliffs, NJ (US); Todd Cicchi, Englewood Cliffs, NJ (US); Patrick Bybee, Englewood Cliffs, NJ (US); Henrik Poulsen, Englewood Cliffs, NJ (US)

(73) Assignee: **OE SOLUTIONS AMERICA, INC.,** Ridgefield Park, NJ (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/947,905

(22) Filed: Nov. 20, 2015

(65) **Prior Publication Data**

US 2016/0254866 A1 Sep. 1, 2016

## Related U.S. Application Data

- (60) Provisional application No. 62/082,545, filed on Nov. 20, 2014.

- (51) **Int. Cl. H04B 10/00** (2013.01) **H04B 10/50** (2013.01)

(Continued)

- (52) **U.S. Cl.**CPC ...... *H04B 10/5057* (2013.01); *H01S 5/0687* (2013.01); *H04B 10/503* (2013.01); (Continued)

(10) Patent No.: US 9,722,705 B2

(45) **Date of Patent:** Aug. 1, 2017

## (56) References Cited

## U.S. PATENT DOCUMENTS

6,496,619 B2 \* 12/2002 Naganuma ...... G02B 6/29391 359/342 6,631,146 B2 \* 10/2003 Pontis ...... H01S 5/141 372/20

(Continued)

## FOREIGN PATENT DOCUMENTS

WO 2014014846 1/2014 WO 2014107537 7/2014

## OTHER PUBLICATIONS

"Control of Widely Tunable SSG-DBR Lasers for Dense Wavelenght Division Multiplexing", by Gert Sarlet, et al., vol. 18, No. 8, Aug. 2000, pp. 1128-1138.

(Continued)

Primary Examiner — Hibret Woldekidan (74) Attorney, Agent, or Firm — Ichthus International Law, PLLC

## (57) ABSTRACT

An apparatus for controlling, monitoring, and communicating with an optical device, photonic integrated circuit or subassembly is provided. The apparatus includes an optical device or subassembly; and afield programmable device including programmable hardware gates coupled to the optical device or subassembly. The field programmable device may be configured to implement a plurality of functions at a gate level for controlling, monitoring, and/or communicating with the optical device or subassembly, each of the plurality of functions being configured to execute as a concurrent process, without use of a microprocessor or a microcontroller. Further, a programmable optical device, such as a programmable optical transmitter, optical subas

(Continued)

sembly, or transceiver based on a tunable laser having field programmable device centric control systems with softwareenabled features offer extensive real-time control and monitoring functionality based on for example actual traffic flows.

## 20 Claims, 33 Drawing Sheets

| (51) | Int. Cl.                                                                    |  |  |  |

|------|-----------------------------------------------------------------------------|--|--|--|

|      | <b>H04B 10/572</b> (2013.01)                                                |  |  |  |

|      | <b>H01S 5/0687</b> (2006.01)                                                |  |  |  |

|      | H01S 5/00 (2006.01)                                                         |  |  |  |

| (52) | U.S. Cl.                                                                    |  |  |  |

|      | CPC                                                                         |  |  |  |

|      | (2013.01); <i>H01S 5/0085</i> (2013.01)                                     |  |  |  |

| (58) | Field of Classification Search<br>CPC H01S 5/0014; H01S 5/0683; H01S 5/125; |  |  |  |

|      |                                                                             |  |  |  |

|      | H01S 5/005; H01S 5/0085; H04J                                               |  |  |  |

|      | 14/0227; H04L 12/2602                                                       |  |  |  |

|      | USPC 398/182, 192–198, 164, 140; 372/29.01,                                 |  |  |  |

|      | 372/29.011, 20                                                              |  |  |  |

|      | See application file for complete search history.                           |  |  |  |

## (56) **References Cited**

## U.S. PATENT DOCUMENTS

| 6,690,693 B1* | 2/2004  | Crowder B82Y 20/00              |

|---------------|---------|---------------------------------|

| 6.788.719 B2* | 9/2004  | 372/29.01<br>Crowder B82Y 20/00 |

|               |         | 372/29.015<br>Koller H01S 3/13  |

| , ,           |         | 372/20                          |

| 6,954,476 B2* | 10/2005 | Coldren B82Y 20/00 372/29.015   |

| 7.061.042    | D2 * | 6/2006  | Coldner H018 5/0014    |

|--------------|------|---------|------------------------|

| 7,061,943    | DZ . | 0/2000  | Coldren H01S 5/0014    |

| T (22 0 52   | D1 * | 11/2000 | 372/18                 |

| 7,622,952    | BI.  | 11/2009 | Lim G06F 1/10          |

|              |      |         | 326/39                 |

| 8,036,540    | B2 * | 10/2011 | Ichino H04B 10/572     |

|              |      |         | 372/38.01              |

| 8,644,713    |      | 2/2014  | Poulsen et al.         |

| 8,964,806    | B2 * | 2/2015  | Ensher H01S 5/06256    |

|              |      |         | 372/20                 |

| 9,438,347    | B2 * | 9/2016  | Conger H04B 10/40      |

| 9,467,229    | B2 * | 10/2016 | Kai H04B 10/2575       |

| 9,485,021    | B2 * | 11/2016 | Bujanos H04B 10/07955  |

| 9,543,737    | B2 * | 1/2017  | Blumenthal H01S 5/0683 |

| 2004/0120372 | A1   | 6/2004  | Simsarian et al.       |

| 2004/0126057 | A1*  | 7/2004  | Yoo B82Y 20/00         |

|              |      |         | 385/16                 |

| 2005/0100065 | A1   | 5/2005  | Coldren et al.         |

| 2006/0072634 | A1   | 4/2006  | Daiber                 |

| 2011/0116792 | A1   | 5/2011  | Blumenthal et al.      |

| 2013/0243015 | A1   | 9/2013  | Eriksson et al.        |

| 2014/0147130 | A1   | 5/2014  | Poulsen et al.         |

| 2014/0236527 | A1*  | 8/2014  | Chan G01R 31/31830     |

|              |      |         | 702/119                |

| 2015/0333475 | A1   | 11/2015 | Blumenthal             |

| 2015/0365177 | A1   | 12/2015 | Blumenthal et al.      |

|              |      |         |                        |

## OTHER PUBLICATIONS

International Search Report and Written Opinion, mailed Mar. 16,

"An FPGA-Based Optical Transformer Design Using Real-Time DSP for Advanced Signal Formats and Electronic Predistortion", by Watts P. et al., Journal of Llghtwave Technology, IEEE Service Cneter, New York, NY, vol. 25, No. 10, pp. 3089-3099

"Design of Digital Pound-Drever-Hall Frequency Stabilizing System for Two-Cavity Dual-Frequency Nd: YAG:laser". By King, Junhong, et al., Eighth Int'l. Symposium on Precision Engineering Measurement and Instrumentation, Proceedings of SPIE, vol. 8759, 875941.

<sup>\*</sup> cited by examiner

FIG. 2

FIG. 4

Mirror 2 sample count

Mirror 2 sample count

At 40°C

Mirror 2 sample count

FIG. 8A

833

Aug. 1, 2017

FIG. 94

## HG. 10A

## HG. IA

5

91 91

R0 = detector circuit impedance at W0.

Digital Wavelength Locking

-2031

Etalon

Circulator

**U-Laser**

DAC Control

Phase Offset

offset from wavelength table

Default

-2037

Phase

-2055

-2053

-2051

-2058

Detector

Filter

Maximum/ Minimum

New Phase Offset Search

2035

-2058

-2059

Detector

-2039

-2033

Etalon Transmitted Power ADC Etalon Reflected Power

Phase Dither

FIG. 20

FPGA Discrete Time Domain PID Loop

Bytes - Wavelength Control

| U)            |

|---------------|

| Se            |

| 22            |

| - <del></del> |

| Ω.,           |

| <b>`</b> ~    |

| .£            |

|               |

| _             |

| -60           |

| $\cup$        |

| aser          |

| õ             |

| Ś             |

| ಥ             |

|               |

| - 1           |

|               |

| بنسب          |

|               |

| $\sim$        |

|               |

| 00]           |

|               |

|               |

[02,03] - Back Mirror

[04,05] - Gain

[06,07] - Gain 2

[08,09] - Front Mirror

[12,13] - SOA2 [10,11] - SOA1

[14,15] - MZM 1 Bias Voltage

[18,19] - MZM 1 Drive Voltage [16,17] - MZM 2 Bias Voltage

[20,21] - MZM 2 Drive Voltage [22,23] - MZM Delay Control

[22,23] - Phase1

[24,25] - Phase2

[26,27] - Available for future use

[28,29] - Available for future use

[30,31] - Available for future use

0x72000-0x80000

Open Memory Space

# MX25L4006E Flash Memory Map

0x00000-0x26FFF

Extra Configuration File Space

0x27000-0x69FFF

Open Memory Space

0x70000-0x70FFF

Non Volatile Register Map Storage

0x71000-0x71FFF

Wavelength Table Storage

## FIG. 24

1

## METHOD AND APPARATUS FOR CONTROLLING, MONITORING, AND COMMUNICATING WITH TUNABLE OPTICAL DEVICES AND SUBASSEMBLIES

## CLAIM OF PRIORITY UNDER 35 U.S.C. §119

This patent application claims benefit of U.S. Provisional Patent Application Ser. No. 62/082,545 filed on Nov. 20, 2014, titled "Methods and Apparatus for Controlling Tunable Optical Devices and Subassemblies," the entire disclosure of which is incorporated herein by reference in its entirety.

## BACKGROUND

Today's fiber optic based networks use transceivers as the interface between electronics and optical signals that propagate on the optical fiber and at other points in the network where information is converted between electronic form and optical form.

Optical devices, including optical, photonic and optoelectronic devices and components are used to transmit, code, receive, and decode optical data for transmission on an optical fiber. The optical devices are interfaced to a variety of electronic circuits which are used to control the devices and components, as well as interface data in electronic form on the transmit and receive side, code and decode electronic data, perform other functions like clock recovery and error correction and realize functions required to control an environment of the circuitry including temperature, wavelength and other tunable laser functions and functions of the interface optics and circuits that are used to realize a fully operational tunable laser and tunable subassembly.

Programmable optical devices, such as transmitters, optical subassemblies, and transceivers, based on a tunable laser, require many control systems to support the functions of the 35 tunable laser and support the control, monitoring and communications functionality. A widely tunable laser includes multiple sections, generally including a gain section, a tunable phase section, and tunable mirror sections and in some designs a tunable filter section is also incorporated. 40 Tuning the physical parameters of these sections results in tuning of an output laser wavelength. Other parameters of the tunable laser include an optical data modulator, if it is integrated or not integrated, and other functions like power control, wavelength locking, linewidth narrowing and control, modulation control, higher order modulation, or the like, performance of which may be enhanced using the present disclosure.

Examples of prior art references may include "Control of Widely Tunable SSG-DBR Lasers for Dense Wavelength Division Multiplexing," *Journal of Lightwave Technology*, vol. 18, No. 8, August 2000; U.S. Pat. Nos. 6,954,476; 6,788,719; 6,690,693; and U.S. Pat. App. No. 2004/0120372, the entire disclosures of which are incorporated herein by reference in their entirety.

Known prior art programmable wavelength tunable transmitters, such as transmitter optical subsystem assembly (TOSA), transceivers and other communications optical subassemblies, however, are not programmable in real-time and thus lack flexibility and responsiveness at the optical layer. Further, as the existing devices lack real time programmability, there is a high cost associated with planning, building, operating and maintaining data center networks.

## **SUMMARY**

It is to be understood that both the foregoing general description and the following detailed description are exem2

plary, and are intended to provide further explanation of the present technology or disclosure as described.

The present disclosure relates generally to optical devices and subassemblies, such as optical transceivers, modules and subassemblies as well as laser transmitters and receivers that employ integrated electronics and photonic integrated circuits and combinations thereof. The optical devices and subassemblies contain multiple elements, for example, widely tunable semiconductor lasers integrated on the same substrate with optical modulators and semiconductor optical amplifiers, non-integrated optical and optoelectronic elements, and other measurement and control devices and elements.

In an aspect, an apparatus for controlling, monitoring, and communicating with an optical device, photonic integrated circuit or subassembly for optical communications is provided. The apparatus includes an optical device or subassembly and a field programmable device including programmable hardware gates coupled to the optical device or subassembly. The field programmable device is configured to implement a plurality of functions at a gate level for controlling, monitoring, and/or communicating with the optical device or subassembly, each of the plurality of functions being configured to execute as a concurrent process, without use of a microprocessor or a microcontroller.

In an aspect of the present disclosure, an optical communication system includes an optical device or subassembly comprising a tunable laser integrated on a same substrate with an optical modulator and a semiconductor optical amplifier, non-integrated optical and optoelectronic elements; and a field programmable device including programmable hardware gates coupled to the optical device or subassembly and the laser transmitter and receiver. The field programmable device is configured to implement a plurality of functions at a gate level for controlling, monitoring, and/or communicating with the optical device or subassembly, each of the plurality of functions being configured to run as a concurrent process, without use of a microprocessor or a microcontroller. The field programmable device of the optical communication system comprises one or more field programmable gate arrays (FPGAs) or programmable logic devices (PLDs). Further, the field programmable device of the optical communication system may be configured to comprise application programmable interfaces (APIs) for real-time control and monitoring of the optical device and subassembly based on actual traffic flows. Also, the plurality of functions may be configured to run at different clock signals in the field programmable device. Further, the field programmable device may comprise a communication interface including one or both of sockets to a graphical user interface (GUI) or an application programming interface (API) that allows control, monitoring and/or communication with the tunable laser integrated on the same substrate with the optical modulator and the semiconductor optical amplifier, non-integrated optical and optoelectronic elements.

In another aspect, the present disclosure comprises real-time programmable optical devices and subassemblies, such as wavelength tunable transmitters (e.g., TOSA), transceivers, and other communications optical subassemblies. According to the present disclosure, software-enabled features, accessible via application programmable interfaces (APIs), offer extensive real-time control and monitoring of the optical devices and subassemblies based on, for example, actual traffic flows. Programmability enables an unprecedented level of flexibility and responsiveness at the optical layer with real-time scaling and rerouting of bandwidth, higher bandwidth extraction from a given fiber plant

as well as a reduction in complexity and related cost of planning, building, operating and maintaining data center networks

In an aspect of the present disclosure, programmable systems, methods and devices are provided to control, 5 monitor and communicate with tunable lasers, tunable transmitters, tunable transceiver pluggables and subassemblies, and board mounted tunable transceivers and the auxiliary integrated or non-integrated optics, optoelectronics and/or electronics. The systems, methods and devices described 10 herein realize functions to design, build, produce and manufacture a fully functional tunable laser, tunable transmitter, tunable transceiver, pluggable, subassembly or board mount. The present disclosure implements monitoring and control and communications functions for the tunable laser, trans- 15 ceiver, module or optical subassembly in a field programmable device including a field programmable gate array (FPGA) or programmable logic device (PLD) circuitry architecture, or in combination with a microprocessor or microcontroller.

Both the FPGA and PLD circuitry are reconfigurable circuitry, which can be programmed/re-programmed in the field and/or real-time after manufacture. According to the present disclosure, the control functions of the optical device or subassembly can be implemented without a microcon- 25 troller or microprocessor. For example, various functions including control functions may be embedded in the FPGA or PLD. By way of example, the functions that are embedded in the FPGA or PLD include, but are not limited to, soft state machines, electronic filters, control and feedback 30 loops, decisions circuits, communications interfaces, etc., which are implemented by embedding concurrent processes in the FPGA, the PLD or the combination of programmable logic and microprocessor. The present disclosure is an advance over existing technologies that utilize microproces- 35 sors or microcontrollers for control and programmable logic devices such as FPGAs or PLDs to store calibration and other data for lookup operation(s).

Other advantages of the present disclosure are described in further detail below. By way of example, the control, 40 monitoring and communications functions to build and operate a tunable transmitter, tunable laser, tunable transceiver, pluggable or subassembly may be programmed in hardware gates in the FPGA, using firmware, each running at their own clock speed and implemented modularly. The 45 concurrency, modularity, ability to run processes at different clock speeds, may result in advances over the existing technology for reduced costs, complexity, power consumption, and other advantages.

The present disclosure includes, but is not limited to, the 50 control, monitor and communications method and apparatus for a tunable laser/transceiver which is programmable and firmware updatable, and may be fully FPGA controlled (no microprocessor or microcontroller required). Embodiments of the present disclosure may include, but are not limited to: 55

Communications interfaces to/from a client or host or fiber communications channel;

Tunable laser wavelength memory and management; Programmable read only memory (PROM)-serial peripheral interface (SPI) FLASH interface to external erasable programmable read-only memory (EPROM);

Set currents and voltages for all control and monitoring functions for the tunable laser, modulator, optoelectronics, electronics, sensors and other control and monitor points that interface via voltages and currents;

Optical and electronic and photonic integrated circuit (PIC) monitors;

4

Boxcar averagers and other signal processing functions; Automatic optical power control;

Wavelength locking;

Linewidth narrowing algorithms and circuits (e.g., Pound Dreyer Hall (PDH));

Temperature monitoring and control;

Alarm and monitoring control and communications;

Application programmable interfaces (APIs); and

Fully calibrated stand-alone, ready for integration into pluggables or on-board—digital control/monitoring/data—onboard calibrated EPROM.

According to an aspect of the present disclosure, control systems and methods are provided to rapidly control an optical device and/or subassembly. The control systems and methods comprise functionality to control elements of the optical device or subassembly, such as a tunable laser, internal and external optical and optoelectronic monitoring and control functions, internal and external electronic monitoring and control functions, signal processing functions, and associated functions in a transceiver, optical module and/or optical subassembly.

According to another aspect of the present disclosure is an implementation of the embodiments of the control systems and methods according to the present disclosure in a field programmable device, such as a FPGA, PLD, or the like, either stand alone or in combination with a microcontroller, and/or in combination with analog to digital converting (ADC) and digital to analog converting (DAC) circuits, where the FPGA, PLD, or the like is used for the control functions as part of the first embodiment, beyond the simple present day use of FPGAs and PLDs as data storage only mechanisms, for example, lookup tables for tunable lasers. This embodiment of the present disclosure thus provides various advantageous over the existing technology, which utilizes FPGAs and/or PLDs in a limited capacity to store data about tunable lasers and other embodiments to be accessed by other processing modules for monitoring, control and processing, but not for the control systems and methods as described herein.

In an aspect of the present disclosure, the field programmable device may be configured to automatically adapt laser control currents of a tunable laser to measured temperature so as to reduce a load on a thermoelectric cooler (TEC), based on the measured temperature and at least one of: by moving between tables stored in the field programmable device or by extrapolating between temperature wavelength maps.

An advantage of using the field programmable device, such as the FPGA, PLD, or the like, as part of the control systems and methods according to the present disclosure is that code and processes may be modular and/or concurrent processes, each may run at different, unique clocks speeds within the same device and is reprogrammable, and can handle all control, monitoring, and communication embodiments. Accordingly, in an aspect of the present disclosure, one or more submodules of the system can be replaced, modified, programmed, and/or re-programmed without affecting other modules/submodules. As such, advantages of running the control, monitoring, and communications systems of the optical devices and subassemblies in a programmable manner at a gate level may include lower power consumption, lower cost, wider use across broader classes of applications, and introduction of new control modules of a variety of types (filter, analog circuits, state machines, etc.) 65 in a common programmable architecture.

According to another of the present disclosure, the methods and systems described herein may be utilized with a

multi-facet laser architecture, as described in U.S. patent application Ser. No. 14/146,717, published on Jul. 10, 2014 as WO2014/107537, which is incorporated herein by reference in its entirety. As described in WO2014/107537, two or more facet of a tunable laser may be used for an output and 5 may be connected to a novel modulator structure. The control and monitoring described in the present disclosure, in certain forms, may have additional advantages over prior state of the art when combined with the inventions described in WO2014/107537.

According to an aspect, the present disclosure may be employed with optical devices and subassemblies that use an FPGA centric architecture. Examples of devices and subassemblies may include U.S. Pat. No. 8,644,713, and U.S. patent application Ser. No. 14/171,480, titled "Program- 15 mable Optical Subassemblies and Modules"; Ser. No. 12/945,470, titled "Optical Network Interface Module Using A Hardware Programmable Optical Network"; and Ser. No. 13/942,519, titled "Control Systems for Optical Devices and Subassemblies," which are incorporated herein by reference 20 device in accordance with an aspect of the present discloin their entirety. The FPGA centric architecture may run all control, monitoring, communications, algorithms using an internal FPGA without use of a microprocessor or microcontroller in these optical devices and subassemblies.

According to the present disclosure, the same firmware 25 for an external FPGA may also be used to calibrate the laser and significantly speed up the calibration speed, where the resulting calibration data is then ported to a wavelength control FPGA which is used to control the tunable laser, making the calibration during manufacturing and the control 30 and re-calibration or re-programming uniform with FPGA technology and firmware across all embodiments of the use of a tunable laser from manufacturing to deployment in a network. As such, the present technology may significantly cut down on the cost of manufacturing and ownership as 35 well as improving performance.

According to another aspect of the present disclosure, a communications interface may be integrated into the field programmable device (e.g., FPGA) as described in U.S. patent application Ser. No. 12/945,470, which is incorpo- 40 rated herein by reference in its entirety, as well as associated patents and patent applications. The communications interface may comprise sockets to graphical users interfaces (GUIs) and/or application programmable interfaces (API) that allow software control, monitoring and calibration of a 45 complete tunable laser using a software layer that interacts with the tunable laser through the field programmable device (e.g. FPGA or PLD or the like) to implement one of any of the fast wavelength calibration algorithms, making the ease of use, manufacturability, speed of calibration, and integra- 50 tion into other manufacturing, system integration and network operation systems enabled and significantly lower cost and flexible compared to any existing approach. The speed of the calibration routines, on the order of minutes, may even allow recalibration in the field or real-time using the appli- 55 cation layer interfaces via the field programmable device (e.g., FPGA, PLD or the like).

In another aspect of the present disclosure, the field programmable device may be configured to receive one or more control signals from a GUI coupled to the field 60 programmable device via wireless communications or from a GUI of another apparatus located at a remote site over an optical communication link.

Other significant advantages of the present disclosure may also include the ability to utilize processes embedded in the 65 field programmable device (e.g., FPGA, PLD or the like), in addition to control and monitoring interfaces, to realize all

6

functions needed to improve the performance of the tunable laser and transmitter using firmware, for example, narrowing a laser linewidth for coherent communications, reducing the laser relative intensity noise (RIN), as two of many examples. These processes may be run in parallel with all other processes for the tunable laser, transmitter, transceiver, module or subassembly, and in many cases can re-use hardware used for other functions.

#### BRIEF DESCRIPTION OF THE DRAWINGS

A more detailed understanding may be obtained from the following description in conjunction with the accompanying drawings.

FIG. 1A illustrates a block diagram conceptually showing components for a field programmable device centric control system in accordance with an aspect of the present disclo-

FIG. 1B illustrates an example of a field programmable

FIG. 1C illustrates an example of how functions are implemented as concurrent, independent processes in the field programmable device.

FIG. 2 illustrates a typical implementation of a tunable laser or transceiver control, monitor, and communications using a microprocessor or microcontroller based architec-

FIG. 3 illustrates an example of an implementation of a Register Write operation in accordance with an aspect of the present disclosure.

FIG. 4 illustrates an example of a block diagram of a photonic integrated circuit (PIC) tunable modulator.

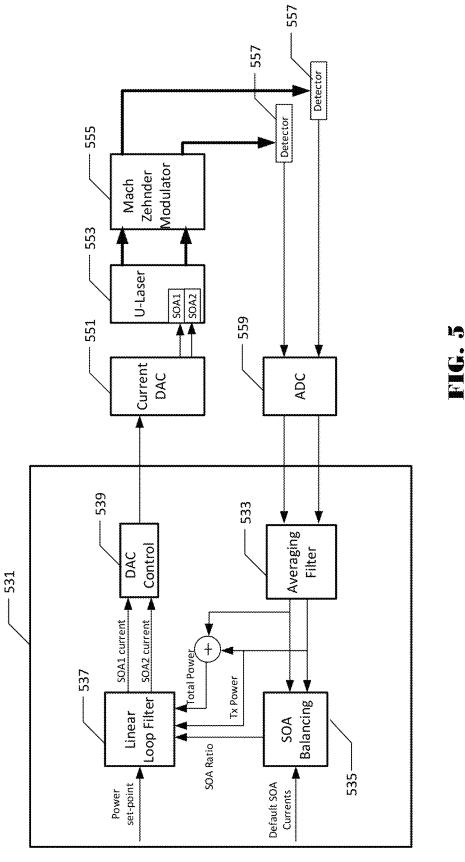

FIG. 5 is an example block diagram of an external control function or loop using the field programmable device technology in accordance with an aspect of the present disclosure.

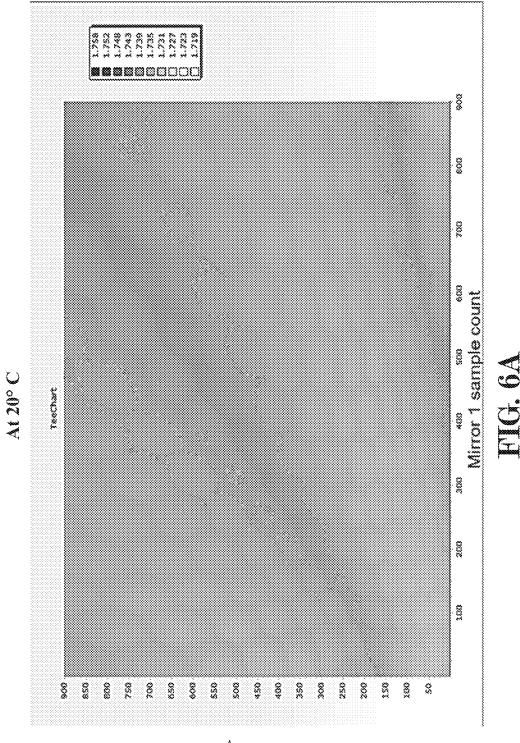

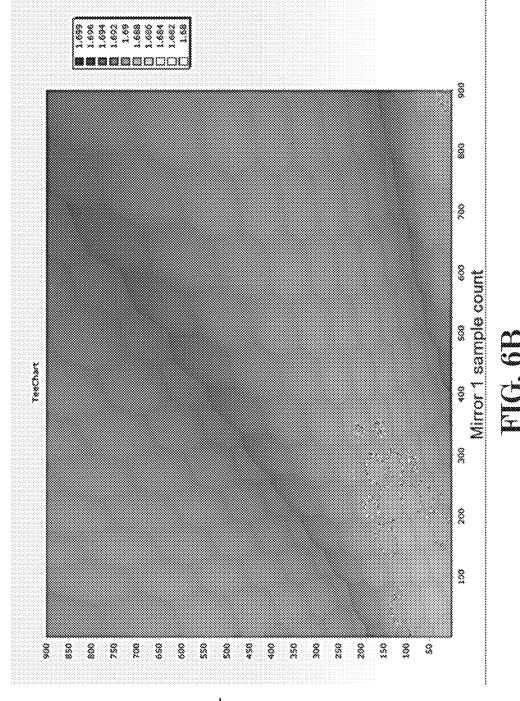

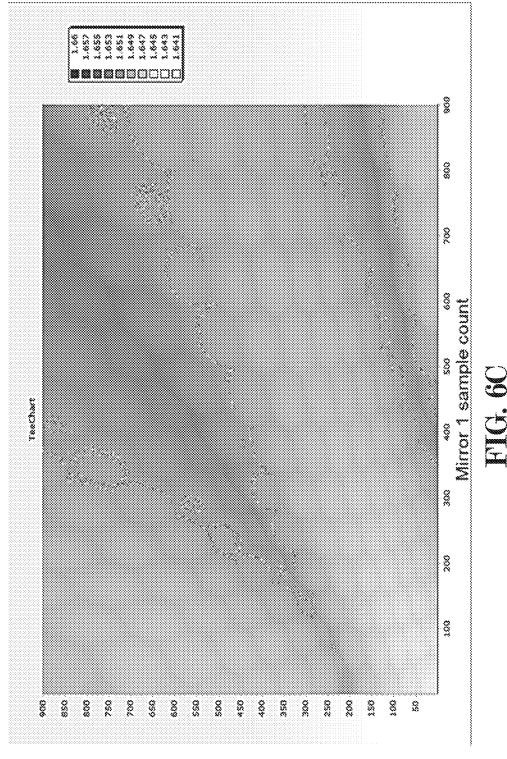

FIGS. 6A-6C illustrate examples of gain voltage maps obtained by tuning laser mirror currents of a tunable laser at three different temperatures in accordance with an aspect of the present disclosure.

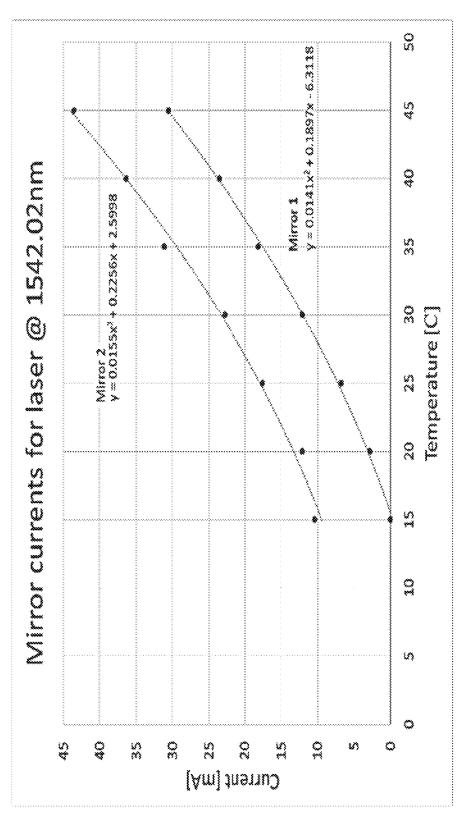

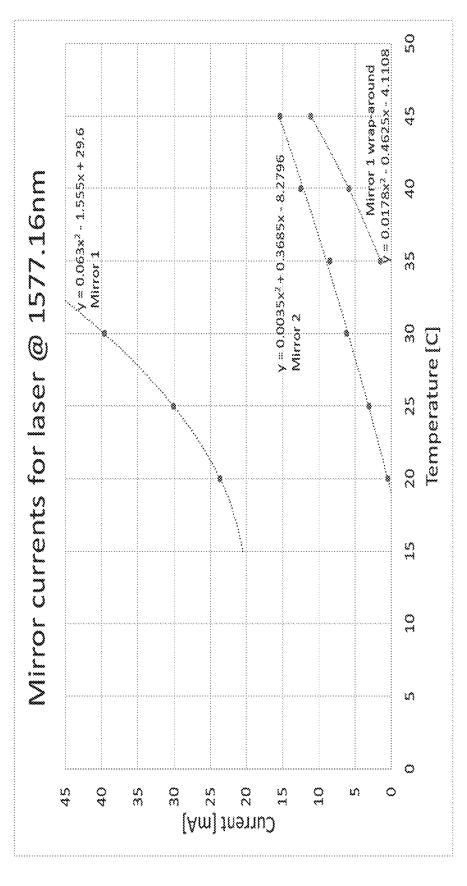

FIGS. 7A and 7B are examples of tuning approximations for two laser mirror currents at 1542.02 nm and 1577.16 nm wavelengths versus temperature.

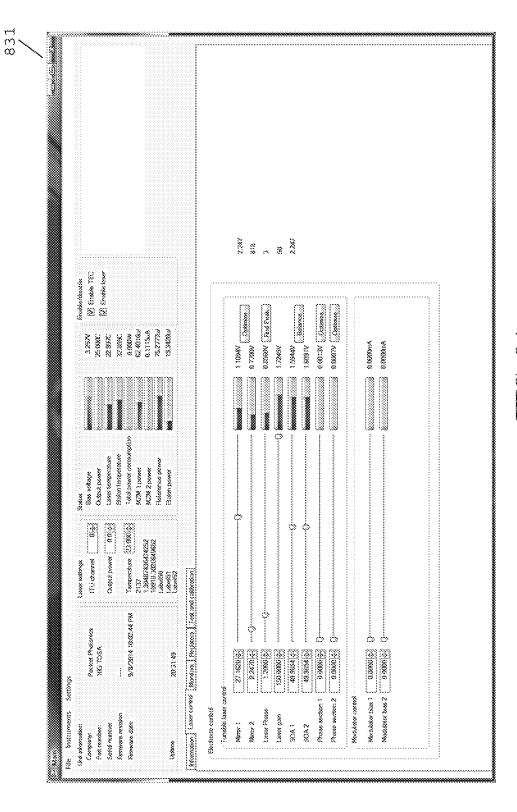

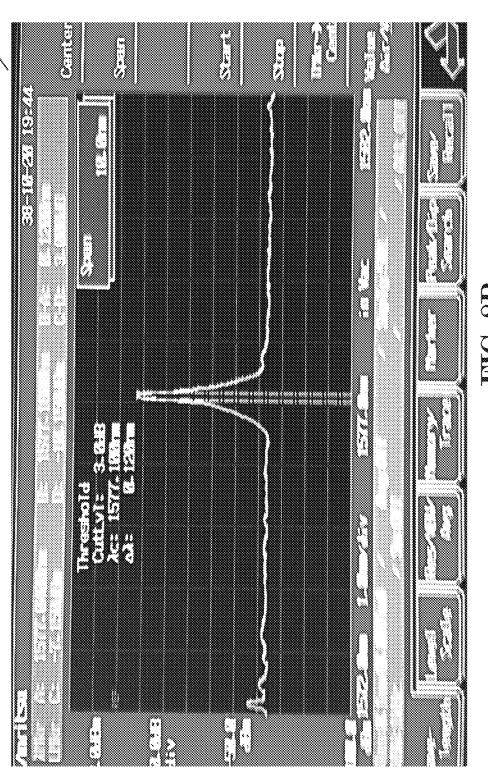

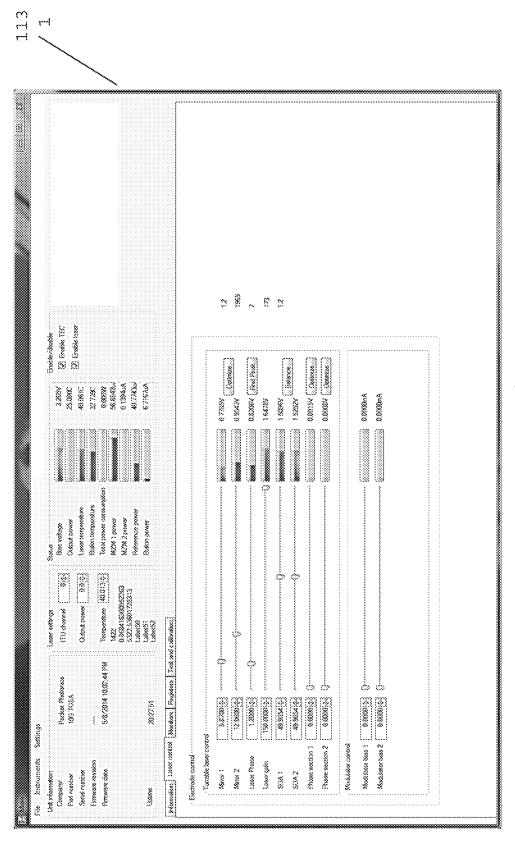

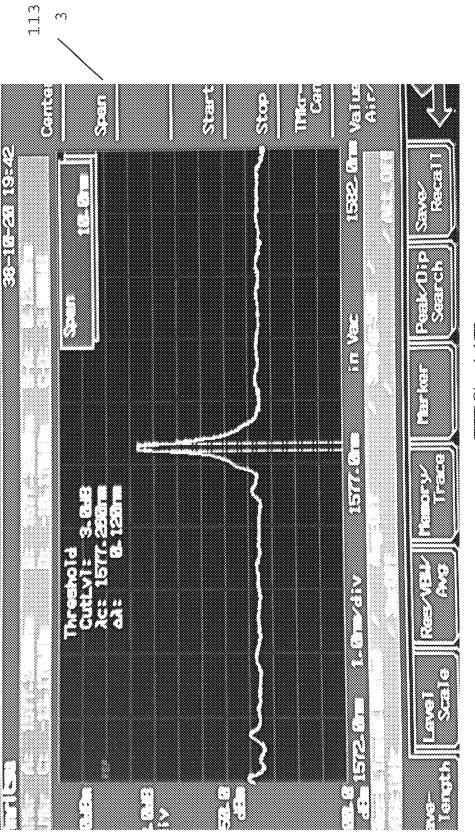

FIGS. 8A-11B illustrate examples of graphical user interfaces (GUIs) that are configured to communicate through processes running in a field programmable device.

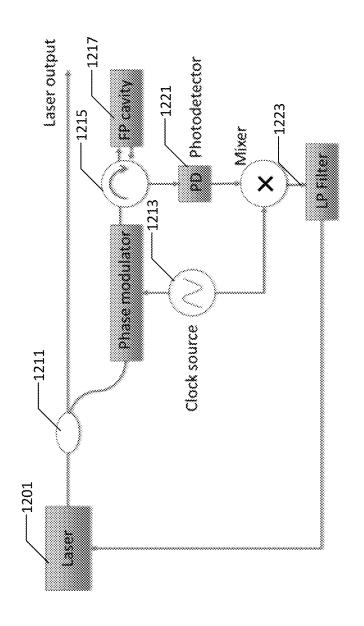

FIG. 12 illustrates a typical implementation of an analog PDH control system.

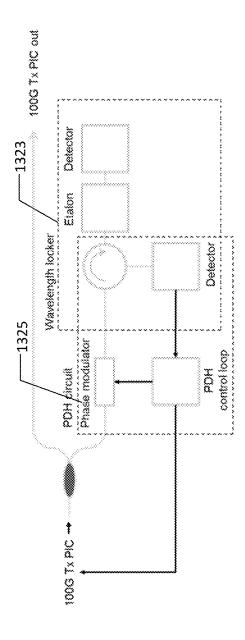

FIG. 13 illustrates an example implementation of a PDH feedback loop in accordance with an aspect of the present disclosure.

FIG. 14 illustrates an example implementation of a PDH algorithm in accordance with an aspect of the present

FIG. 15 illustrates an example implementation of the PDH algorithm in accordance with an aspect of the present disclosure.

FIG. 16 shows an example of an equation for detected power from an etalon reflected optical signal in accordance with an aspect of the present disclosure.

FIG. 17 illustrates an example implementation of the PDH algorithm in accordance with an aspect of the present disclosure.

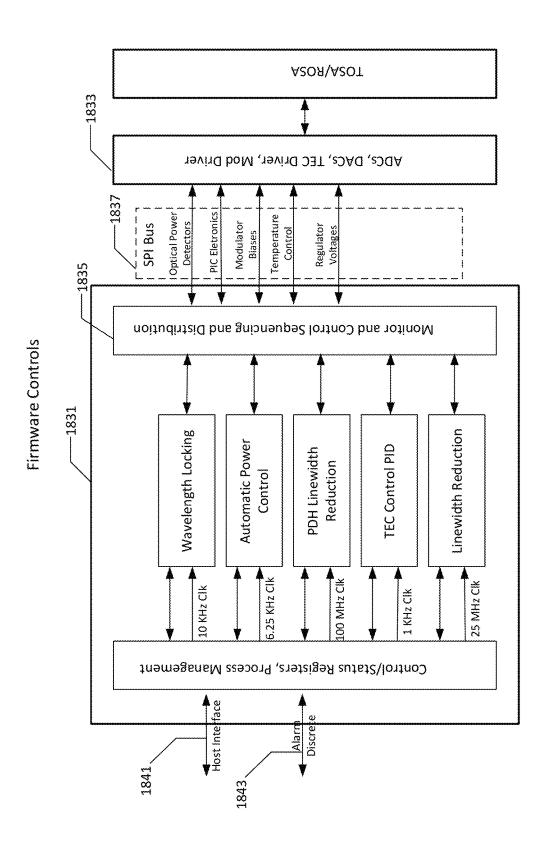

FIG. 18 illustrates an example block diagram of firmware control of a field programmable device and other devices in accordance with an aspect of the present disclosure.

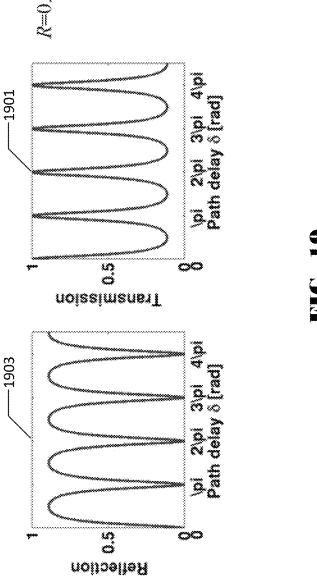

FIG. 19 illustrates an example of general etalon reflected and transmitted responses in accordance with an aspect of the present disclosure.

FIG. **20** illustrates an example of a block diagram illustrating an example implementation of a wavelength locking algorithm, in accordance with an aspect of the present disclosure.

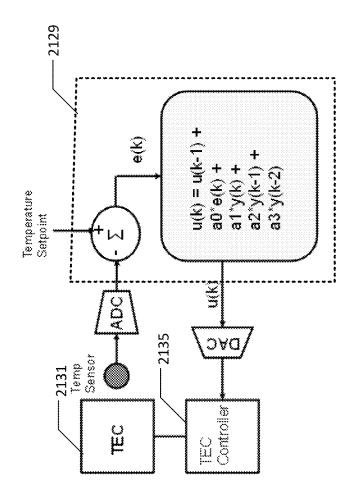

FIG. 21 illustrates an example diagram of one implementation of a temperature control process in accordance with an aspect of the present disclosure.

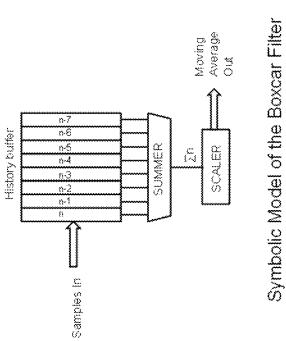

FIG. 22 illustrates a block diagram of a symbolic model of one channel of the boxcar filter in accordance with an aspect of the present disclosure.

FIG. **23**A illustrates an example address spacing of a flash memory in accordance with an aspect of the present disclo- 15 sure.

FIG. 23B illustrates an example of a wavelength definition table in accordance with an aspect of the present disclosure.

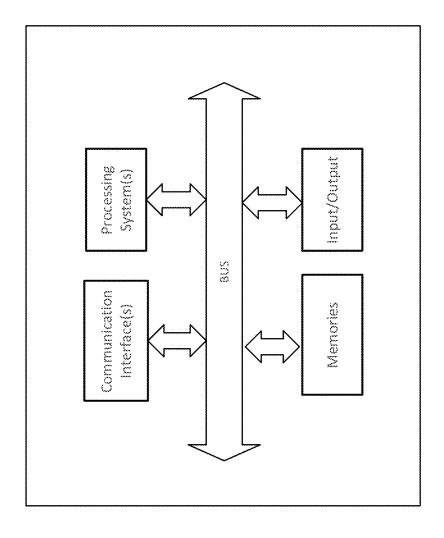

FIG. **24** illustrates an example of an implementation of <sup>20</sup> one or more processing systems in accordance with an aspect of the present disclosure.

#### DETAILED DESCRIPTION

According to the present disclosure, optical devices, such as optical transmitters, optical subassemblies, and transceivers which are programmable are described. By way of example, the programmable optical devices are based on a tunable laser having field programmable device centric (e.g., 30 a FPGA or a PLD centric) control systems which support various functions of the tunable laser and supporting control, monitoring and communications functionality. The present disclosure comprises real-time programmable wavelength tunable transmitters, such as transmitter optical subassemblies (TOSAs), transceivers, and other communications optical subassemblies.

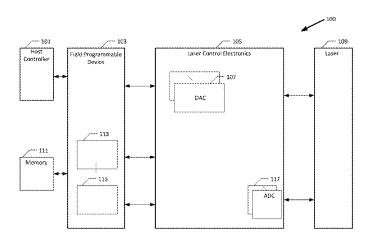

FIG. 1A illustrates a block diagram conceptually showing components for a field programmable device centric (e.g., FPGA/PLD centric) control system. A system 100 shown in 40 FIG. 1 includes a host controller 101, a field programmable device 103 (e.g., FPGA, PLD or the like), laser control electronics 105, a tunable laser 109, and a storage 111. The host controller 101 may be configured to communicate with the field programmable device 103 for various functions, 45 and also configured to receive data relating to operation of the tunable laser 109. In the example, the field programmable device 103 may drive the laser control electrodes 105 through digital-to-analog converters (DACs) 107 interfaced to the field programmable device 103 and the tunable laser 50 109. Further, the field programmable device 103 may be coupled to the tunable laser 109 through analog-to-digital converters (ADCs) 117 for communications and control of the tunable laser 109.

Further, the field programmable device 103 may also 55 include various components, modules or processes (which are not shown in FIG. 1A, but described herein in detail), such as communication interfaces to/from a client or host for fiber communications channel; tunable laser wavelength memory and management; PROM-SPI Flash interface to 60 external memory; setting currents and voltages for all control and monitoring functions for the tunable laser, modulator, optoelectronics, sensor and other control and monitor points that interface via voltages and currents; optical and electronic and photonic integrated circuit (PIC) monitors; 65 boxcar averagers and signal processing functions; automatic optical power control; wavelength locking; linewidth nar-

8

rowing functions, temperature monitoring and control; alarm and monitoring control and communications; application programming interfaces (APIs); and many other functions for implementing various aspects of the present methodology described herein. Further, the field programmable device 103 may include an internal storage (not shown) and/or an external storage such as the storage or memory 111 coupled to the field programmable device 103 for storing various parameters including parameters for implementing various aspects of the present technology. In an aspect of the present disclosure, the memory 111 may include one or more look-up tables of data in connection with implementing various aspects of the present technology described herein.

Further, in an aspect of the present disclosure, a field programmable device-centric architecture (e.g., FPGA, PLD or the like centric) may be implemented as follows. The host controller 101 may transfer code for one or more algorithms, modules, processes or functions to the field programmable device 103, either as high level programming language (e.g., C code or the like) in an embedded soft processor, or for even more efficiency and high speed, as hardware description language (e.g., HDL code or the like). The host computer 101 may also be connected through a standard interface, i.e., a universal serial bus (USB) connection, to the field programmable device 103. As noted, while performing various aspects of the present technology, the field programmable device 103 may communicate directly with DACs 117 that are configured to drive currents to various components including laser mirrors of the tunable laser 109 and communicates with ADCs 107 that are configured to monitor the electrode voltages and/or power detectors to collect data from the tunable laser 109 in accordance with various aspects of the present technology. Alternatively, and/or in addition to, the field programmable device 103 may control transients in laser temperature by monitoring a thermistor on the tunable laser 109 and driving a current control input to a TEC controller of the tunable laser 109. Further, the field programmable device 103 may buffer or store data relating to controlling, monitoring, and communicating with the tunable laser 109 in one or more storage devices, such as the memory 111, whether it is internal or external to the field programmable device 103, to perform various functions, methods, algorithms or methodologies, in accordance with aspects of the present disclosure.

In an aspect of the present disclosure, the present technology may be viewed as a field programmable device (e.g., FPGA, PLD or the like) centric architecture for optical communications systems. As such, the one or more implementations of the present technology may be optimized for a hardware architecture and the methodology or algorithm itself, incurring negligible overhead in the processing of various aspects of the present technology in the field programmable device 103, and thus data transfers to and from the coupled ADCs 107, DACs 117, and storage 111 may be very efficient.

In another aspect, the present disclosure provides soft-ware-enabled features accessible via application program-mable interfaces (APIs), offering extensive real-time control and monitoring of one or more modules or processes based on, for example, actual traffic flows. Such programmability provides an unprecedented level of flexibility and responsiveness at an optical layer with real-time scaling and rerouting of a bandwidth, a higher bandwidth extraction from a given fiber plant as well as a reduction in complexity and related cost of planning, building, operating and maintaining data center networks. Rapid control of all aspects of

a tunable laser, in which more than one facet are optically available, or integrated transmitter photonic integrated circuit (PIC) assembly that combines a tunable laser and modulator, or optical transceiver or optical subassembly is provided. That is, the present disclosure may provide control 5 which is modular, concurrent, independent processes, fast and reprogrammable, and thus may handle all control, monitoring, and communication aspects, in which any submodule of a system may be replaced, modified, programmed without affecting other modules or processes. In other 10 words, in an aspect, the control, monitoring, and communications system may comprises modular, independent, and/ or concurrent processes configured to run in the field programmable device, each of which may be configured to run at different clocks. The advantage of running all control, 15 monitoring and communications in a programmable manner at a gate level may result in lower power, lower cost, wider use across a broader classes of applications, and introduction of new control modules of a variety of types (filter, analog circuits, state machines, etc.) in a common programmable 20

As such, the present disclosure may provide for control, monitoring, communications, and algorithm implementations using an internal field programmable device such as am FPGA, PLD, or the like, without using a microprocessor 25 or a microcontroller, and may even use the same firmware for an external FPGA, which is used to calibrate a tunable laser, thereby significantly speeding up the calibration speed of the tunable laser. The resulting calibration data may then be ported to a wavelength control FPGA which is used to 30 control the tunable laser, making the calibration during manufacturing and the control and re-calibration or reprogramming uniform with the field programmable device based technology described herein and firmware across all aspects of the use of a tunable laser from manufacturing to 35 deployment in a network, significantly cutting down on the cost of manufacturing and ownership as well as improving

In an aspect of the present disclosure, the communications interface into the field programmable device 103 may pro- 40 vide gate level general programming and interfaces for graphical users interfaces (GUIs) and/or application programmable interfaces (API) that allow software control, monitoring and calibration of a complete tunable laser using a software layer that interacts with the tunable laser through 45 the field programmable device 103 to implement one of any of the algorithms described herein including the fast wavelength calibration algorithms, making the ease of use, manufacturability, speed of calibration, and integration into other manufacturing, system integration and network operation 50 systems enabled and significantly lower cost and make flexible compared to any prior existing technology. The speed of the calibration routines, on the order of minutes, may even allow recalibration in the field or real-time using the application layer interfaces via the field programmable 55 device (e.g., FPGA, PLD or the like).

Advantages of the present disclosure may include, but not limited to, many significant advantages over the existing technology that uses a microcontroller or microprocessor as a main control and an FPGA primarily as a data storage and 60 lookup device. In the past, the performance as a function of footprint and power consumption of field programmable devices such as FGPAs was not considered competitive to microprocessors to handle various functions required for real time data and control in tunable laser applications. 65 However, in recent years, field programmable device technology, including FPGA, PLD, or the like technology, has

10

advanced significantly and has become a preferred and more flexible method and apparatus to control, monitor and communicate than many microcontroller or microprocessor based solutions.

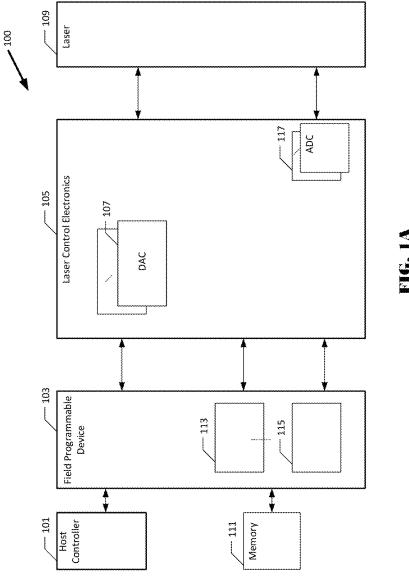

By way of example, as shown in FIG. 1B, a field programmable device such as an FPGA is an integrated circuit that can be programmed in the field or real-time after manufacture, unlike certain integrated circuits such as a microcontroller or a microprocessor, which is hard-core. That is, FPGAs are semiconductor device that are based on a programmable/configurable logic blocs connected via programmable interconnects or wiring circuits, thereby enabling the FPGAs to be reprogrammable to desired application or functionality requirements after manufacturing. In other words, an FPGA is a device based on a gate and device interconnection loaded into the FPGA to operate on data and signals at inputs to generate outputs. In one implementation, the field programmable device 103 may include an FPGA or PLD or the like comprising a plurality of configurable logic blocks (CLBs) 133, a plurality of input/output (I/O) ports 135, programmable interconnect 137, etc. Each configurable logic block 133 (CLB) may include various components, such as carry logic, input look-up tables, flip-flops, etc. The operation of the FPGA as well as the clock speed of different processes running on the FPGA may be changed in real time, and thus a wide variety of control, monitoring, feedback, communications and other functions may be realized with hardware level performance in the FPGA. Thus, by way of example, in accordance with an aspect of the present disclosure, a field programmable device (e.g., FPGA, PLD, or the like) based architecture may enable concurrent control, monitoring, and communications processes for the tunable laser or tunable laser based module.

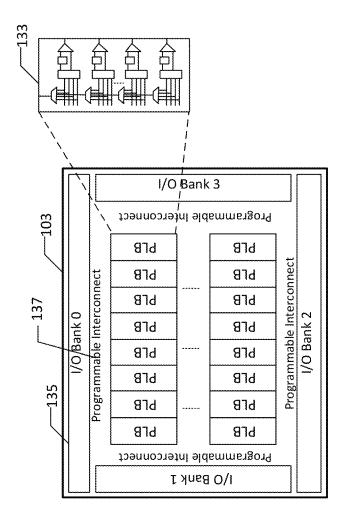

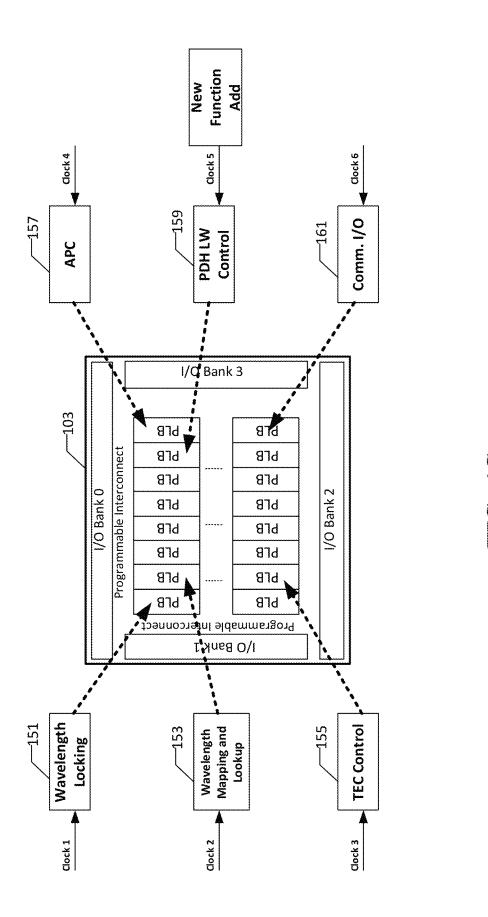

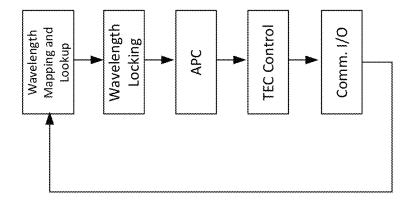

Further, as shown in FIG. 1C, different areas of the FPGA circuitry may be allocated or used to implement different data and/or control functions all within the single device. By way of example, in FIG. 1C, a plurality of data and/or control functions or modules may be implemented in one or more PLBs, e.g., a wavelength locking 151, wavelength mapping and lookup 153, TEC control 155, automatic power control (APC) 157, PHD Linewidth control 159, communications I/O 161, etc., each running at different clock signals, e.g., clock 1, 2, ... 6. Further, a new module or process such as a PDH linewidth (LW) control 159 with a clock signal (e.g., clock 5) may be added in real-time.

In an aspect of the present disclosure, some functions that may be realized in accordance with various aspects of the present technology may include but are not limited to:

Control of optical properties of a data modulated tunable laser including a chirp of a transmitted optical signal and adjusting the control based on an output wavelength of the tunable laser and other parameters;

Temperature monitoring and control of temperature sensitive components (e.g., laser, etalon, etc.);

Control and/or adjustment of a laser output power (e.g., by adjusting gain sections and voltage controlled attenuators);

Control of a laser wavelength of a tunable laser by controlling mirrors, resonators, phase sections and other wavelength tunable elements by embedding a current-wavelength control map, that can also be a function of temperature;

Control and monitoring of a wavelength locker circuit and function. The internal mapping can also be changed in real time in response to calibration and re-calibration of the tunable laser using a wavelength locker;

Functions that require larger memory capabilities of FPGAs, like state size, as compared to microcontrollers or microprocessors:

Concurrent processes that can operate independently of each other leading to a higher performance at a given 5 clock speed compared to serial finite state microprocessors, with higher fault tolerance, ability to manage power by turning on and off processes individually and updating processes individually without having to rewrite and recompile the complete code;

Continual operation upon host failure (e.g., a control interface that in the case that the host fails the unit can still continue to operate);

Corrective action (e.g., if laser output power deteriorates 15 or laser wavelength shifts the FPGA can take corrective action—per locker and other mechanisms); and

Other functions that can be reprogrammed to fit different applications. One chip or a smaller subset of electronic applications and PIC, switches, or transmitter and receiver subassemblies driving up the volume and lower cost and eventually power consumption and size.

As noted above, some examples of the programmable firmware functions that may be implemented in the field 25 programmable device 103 such as the FPGA, PLD or the like, may include but not limited to (functions or examples below may be implemented alone or in combination with others):

Host communications interfaces and memory map;

Wavelength memory and management;

Programmable read-only memory (PROM)-serial peripheral interface (SPI) FLASH interface to external erasable programmable read-only memory (EPROM);

Set currents and voltages;

Optical and electronic and photonic integrated circuit (PIC) monitors;

Boxcar averagers;

Automatic power control;

Wavelength locking;

Linewidth narrowing algorithms (like Pound Dreyer Hall (PDH));

Temperature monitoring and control;

Alarm and monitoring control and communications; and Application programmable interfaces;

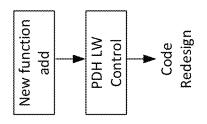

As noted earlier, FIG. 1C illustrates an example of how some of the functions that may be implemented as concurrent, modular processes, while providing an advantage over the existing technology using a microcontroller and/or a serial state machine as shown in FIG. 2, which illustrates a 50 typical implementation of a tunable laser or transceiver control, monitor, and communications using a microprocessor or microcontroller based architecture. As shown, the microprocessor or microcontroller by design executes the functions, modules or processes in a sequential manner, for 55 example, executing the wavelength mapping and lookup 161, wavelength locking 163, APC 165, TEC control 167, and communication I/O 168. Further, if a new function such as a PDH LW control 173 is to be added (at 171), then code need to be redesigned for the microprocessor or microcon- 60

However, as noted above, in accordance with an aspect of the present disclosure, the present technology provides the field programmable device 103 (e.g., FPGA, PLD or the like) which may implement various functions, modules or 65 processes relating to control, monitor, and communication with a tunable laser or transceiver, as concurrent, indepen12

dent modules or processes which are configured to run at different clock signals, without use of the microprocessor or microcontroller.

Host Communication Interfaces and Memory Map

In an aspect of the present disclosure, the field programmable device 103 may include a slave controller that may implement standard serial protocols, such as an Inter-IC bus (I2C) and/or serial peripheral interface (SPI), or other proprietary protocols. The advantage of the present technology over any microprocessor/microcontroller or system-on-chip (SoC) based system is that the slave controller of the present disclosure is not a hard-core, and thus it may easily be modified to suit host interface requirements in the field programmable device 103.

By way of example, in an aspect of the present disclosure, a register map architecture may be based on two dual port chips may therefore be used across a wider variety of 20 random access memories (RAMs), one for a register map and one for wavelength table data which may be implemented in (or external but coupled to) the field programmable device 103. Host read/writes to the register map may then be directly addressed to one port of the register table RAM, while up/download of the wavelength table data is accomplished through a set of registers that include the parameters for a single wave table entry and redirect this data to an appropriate location in a wave table RAM. The second RAM port may be used for updating of digital-toanalog (DAC) data from RAM, reading of analog-to-digital (ADC) monitor data to RAM, and updating of laser/modulator control parameters from the wave table RAM when wavelength is changed or as dictated by a system. Dedicated control logic may perform RAM to ADC/DAC transactions, without the use of a microcontroller or microprocessor. The logic implemented in the field programmable device 103 may be optimized further for transfer efficiency, has predictable latency, and can be tuned to prioritize transactions that require very low latency.

> In another aspect of the present disclosure, a registered memory map of the field programmable device 103 may be implemented within the field programmable device 103 and controlled via a host communication interface. The registered memory map may define a current state of a control system, which in turn determines the wavelength and output power of a tunable laser assembly. The state of a control system may be a result of electrode currents, bias voltages, device operating temperature and various configurable settings associated with the tunable laser like a TEC PID control loop and wavelength locker, for example. All of these individually configurable modules or processes may be changed and monitored by writing to or reading from an appropriate register in the registered memory map of the field programmable device 103, without the use of the microprocessor or microcontroller.

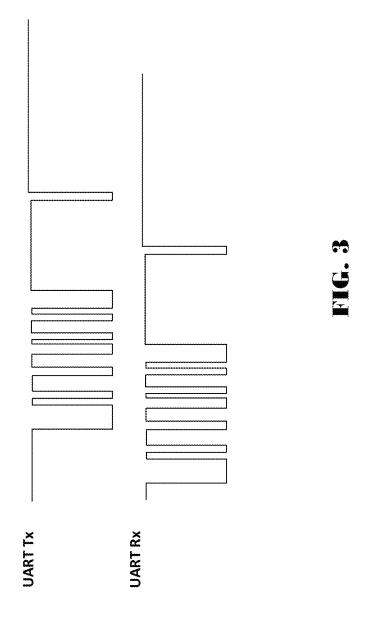

> By way of example, an example implementation of a Register Write operation via UART is shown in FIG. 3. In the implementation, a UART is used to communicate to an I2C device. As shown in FIG. 3, the field programmable device 103 receives a command from a host or host controller 101 via a UART string (e.g., UART Tx from the host to the field programmable device), the UART string is echoed back to the host or host controller (e.g., UART Rx from the field programmable device to the host), the command is then interpreted, and an I2C command is issued to a register interface on the I2C bus coupled to the field programmable device 103. The UART then sends a string

back with the written data. In the implementation, for a register write cycle it may take approximately 1.2 ms.

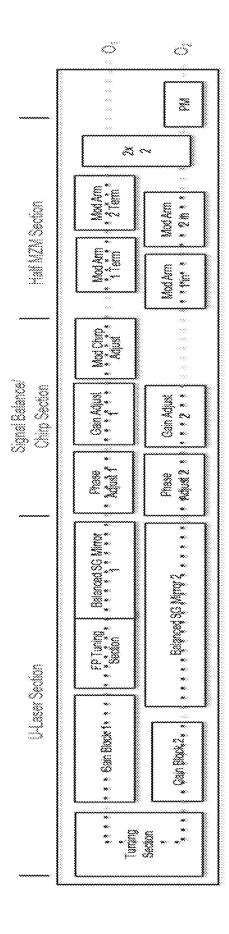

## Automatic Power Control (APC)

In an aspect of the present disclosure, an automatic power control (APC) function or loop may be implemented as a concurrent, independent module or process within the field programmable device 103. An APC control function or loop dynamically maintains a laser output power at a commanded 10 level while also maintaining a ratio of semiconductor optical amplifier (SOA) currents in a tunable laser (e.g., a U-Laser), which in turn maintains a balance of photocurrents in Mach Zehnder modulator legs, which is required for proper modulation. FIG. 4 illustrates a block diagram of an example PIC 15 tunable modulator as described in U.S. Patent Application Ser. No. 61/748,415, published on Jul. 10, 2014 as WO2014/ 107537 with elements that enable APC and the APC loop. Further, an example block diagram of an external control function or loop using the field programmable device tech- 20 nology such as FPGA, PLD or like technology is also shown in FIG. 5.

In an aspect of the present disclosure, a field programmable device 531 (similar to the field programmable device 103 shown in FIG. 1A) may include an averaging filter 533, 25 a SOA balancing 535, a loop filter 537, and a DAC control **539**. In the example, the averaging filter **533**, SOA balancing 535, loop filter 537, and DAC control 539 may all be implemented digitally as one or more concurrent, independent modules or processes within the field programmable 30 device **531**. The field programmable device **531** (e.g., FPGA or PLD or the like technology) is configured to allow performing these functions optimally and with low fixed latency and high noise immunity. Further, in the example, current DAC 551 and ADC 559 may be located outside but 35 coupled to the field programmable device 531, and the field programmable device 531 drives the laser SOA currents to a tunable laser (e.g., U-laser 553) through the external current DAC (e.g., Current DAC 551). The detected optical powers, via detectors 557, from two legs of the Mach 40 Zehnder Modulator 555 may be digitized in the external ADC 559 and input to the field programmable device 531, which first passes them through the averaging filter 533 to smooth a response and filter noise picked up in an analog path.

The filtered detected powers are input to the SOA balancing 535, which starts with default SOA currents provided from a wavelength table (not shown) and then measures the detected powers to determine a proper ratio of SOA currents to maintain balanced MZM outputs. This ratio is fed to the 50 loop filter 537 along with Tx Power, which is the power out of leg 1 of the Mach-Zehnder Modulator 555, and total power, which is a sum of the powers in the two modulator legs. The linear loop filter 537 may be configured to adjust SOA1 and SOA2 currents in fixed steps, while maintaining 55 a ratio of the SOA1 to SOA2 currents until a desired Tx power is attained. An initial step size in the larger of SOA1 or SOA2 may be in 1000 uA increments. When the output power is within one 1000 uA increment, the step size may be reduced to 125 uA and a final "Vernier" search may be 60 performed until the output power is within one 125 uA step. If the measured power changes by more than 2 counts or 250 uA, the Vernier search resumes. If the tunable laser is reinitialized (e.g., turned off and then on), however, a crude search may restart followed by the Vernier search.

It is also noted that theoretically, SOA current may affect laser wavelength tuning and stability through its electrical 14

and thermal effects. When SOA current changes, its control circuits could affect the circuits that control the laser's gain sections, laser phase section and mirror sections, thus affect the wavelength's tuning and stability. In addition, SOA current change could affect the thermal stability around the mirrors, which affects the mirrors' performance, in turn it affects the wavelength tuning and stability.

In one implementation of the APC function in the field programmable device **531**, the SOA power may be adjusted proportionally per wavelength using a real time control loop to maintain output power. Measurements to date have shown that, with the APC and wavelength locker modules operating cooperatively, small incremental adjustments of the SOA may not significantly affect the wavelength.

In an aspect of the present disclosure, the wavelength and power stability may be summarized as examples as below.

| State                         | Power                                              | Wavelength Time                                                          | Comments                                                                       |

|-------------------------------|----------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Off<br>Power-on               | <=-30 dBm<br><=1 mW/s,<br><=1 dB<br>over-<br>shoot | +/-0.9 nm<br>+/-0.2 nm <30 s                                             | APC may be<br>modified to<br>reduce power<br>per specified<br>slope            |

| Active                        | +/-1 dB                                            | +/-25 pm Wave-<br>length<br>tuning<br>2 s                                | stope                                                                          |

| Power-off                     | -2.1 dB                                            | +/-0.3 nm                                                                | Lambda inside<br>mask with<br>indicated<br>vertices as<br>power slopes<br>down |

| Power-off<br>Power-off<br>Off | -5.6 dB<br>-7.6 dB<br><=-30 dBm                    | +/-0.4 nm<br>+/-0.7 nm<br>+/-0.9 nm <=2 ms<br>(DWDM),<br>10 us<br>(SFP+) | Time from full power to off                                                    |

Automatic Wavelength Mapping (AWM)

One of the limiting factors in reducing power consumption of optical laser modules is the need for active temperature stabilization of a laser to keep the lasing wavelength within the specified accuracy. Typically, a laser needs to be stabilized to within  $\pm 0.05^{\circ}$  C., and especially in the extreme regions of a temperature range (a typical temperature range is  $-5^{\circ}$  C. to  $70^{\circ}$  C.) the thermoelectric cooler (TEC) configured to facilitate temperature stabilization may consume a significant amount of power to meet this specification. For example, when the laser needs to be at a temperature of  $20^{\circ}$  C. and the environment is at  $70^{\circ}$  C., meaning that the laser package is at  $80^{\circ}$  C. to  $85^{\circ}$  C., the TEC needs to span a temperature gap of  $60^{\circ}$  C. to  $65^{\circ}$  C.

In an aspect of the present disclosure, a means to reduce a load of the TEC and in some instances completely remove the load may be provided by, instead of keeping laser control currents fixed and stabilizing the laser, letting the laser control currents automatically adapt to the temperature. To exemplify the embodiment further, instead of operating the laser at 20° C., one could operate the laser at 60° C. and thus reduce the gap from the laser temperature to the laser package temperature to 20° C. to 25° C. This may be done "dynamically," based on the measured temperature, and by moving between tables stored a-prior in a field programmable device (531 or 103) such as an FPGA, a PLD or the

like, or extrapolating between temperature wavelength maps using certain algorithms and fit functions. The effects of dynamic temperature setting of a tunable laser may include: (i) overall reduction in power consumption of an optical transmitter since the temperature delta (or difference) 5 between the tunable laser and the case temperature of the optical transmitter may be maintained as small as possible by adjusting a set-temperature of the tunable laser as the case temperature changes, and (ii) a range of an operating temperature of the optical transmitter may be widened compared to the existing technology which sets the laser temperature at a certain temperature value.

FIGS. **6A-6**C show examples of gain-voltage maps obtained by tuning laser mirror currents of a tunable laser at three different temperatures (e.g., 20° C., 30° C., and 40° 15 C.). In this present disclosure, the three different temperatures may be referred to as the calibration temperatures. In an aspect, tuning points or wavelengths are identified using one or more calibration algorithms, such as algorithms described in U.S. patent application Ser. No. 62/073,713, 20 and its corresponding utility patent application, which are incorporated herein by reference in its entirety, for each map and loaded into the FPGA.

For example, FIG. 6A illustrates an example of a gainvoltage map which is obtained by tuning laser mirror 25 currents of a tunable laser having two mirrors at a temperature of 20° C. In the example, the gain-voltage map is generated by observing optical output power as values of two mirror currents are varied. Further, all the minima of the gain-voltage map may be identified, via various processing, 30 as points where the tunable laser is outputting a maximum power, and thus associated wavelengths may be extracted. The extracted wavelengths (or lasing wavelength peaks) may be used for tuning and calibrating processes of the tunable laser. Similarly, at temperatures of 30° C. and 40° C., 35 corresponding gain-voltage maps may be generated respectively as shown in FIGS. 6B and 6C. In the example, it is noted that the gain-voltage maps are different based on the temperature values.

In an aspect of the present disclosure, the automatic 40 wavelength mapping process may be implemented as a concurrent, independent module or process in the field programmable device 103 or 531, and may be configured to enable control loops to use data at different calibration temperatures. The adjustment of tuning currents for the laser mirrors may be done using one or more algorithms, and points from the tuning maps (or the gain-voltage maps) are described in more detail below as well as shown in FIGS. 7A and 7B. From the gain-voltage maps, the temperature dependence of the mirror currents may be estimated and analytical approximations may be derived. The temperature dependence of the mirror currents may then be derived from three or less gain-voltage maps taken at different temperatures given detailed knowledge of the tunable laser itself.

By way of example, the characteristics of the mirror 55 currents,  $I_{mirror}$ , as a function of temperature t, can be accurately approximated by a second order polynomial equation as shown below.

# $I_{mirror}(t)=at^2+bt+c$

where a, b and c are constants that may or may not be specific to a given wavelength and t is the temperature of the laser. Therefore, each channel may or may not require additional parameters associated with it to accurately apply mirror currents with varying temperature.

As noted, in FIGS. 7A and 7B, an example of tuning approximations for the two laser mirror currents at 1542.02

nm and 1577.16 nm wavelengths versus temperature is provided. In the examples of mirror currents, one can observe a continuous current over 30° C. on the left curve and a wrap-around scenario where one mirror current exceeds that maximum allowed current and wraps around as a curve, as shown in a bottom part of FIG. 7B. The latter is in some cases not desirable and thus the continuous example on the left may be the only feasible option for use. There may be thus two options that, if both employed, can avoid the "wrap-around" scenario: (i) when doing gain-voltage scans typically each wavelength is found multiple times and one can thus eliminate some of the wrap-around channels and in addition, (ii) the mirrors can have higher current limitations removing the remaining wrap-around channels. Typically, the latter is avoided to reduce power consumption as the wrap-round is perfectly acceptable when the temperature is fixed (the currents are changed only when a channel is changed and significant current changes are acceptable in this case). When the temperature is not fixed, mirror currents may increase and thus PIC power consumption also increase, as the cost in power is minimal compared to what is saved on the TEC power.

16

Further, it is noted that as can be seen in FIGS. 6A-6C, different gain-voltage maps are observed over different temperatures. Various aspects of the automatic wavelength mapping, tuning and calibration of the tunable laser, as described herein, may be implemented as one or more concurrent, independent modules or processes in the field programmable device 103 or 531, and subsequently be configured to use data (e.g., data relating to the lasing wavelengths and others) at different calibration temperatures. Further, in an aspect of the present disclosure, the gain-voltage maps observed at the different temperatures may be used to determine lasing wavelengths at the different temperatures of the tunable laser. Also, the temperatures of the tunable laser in the field may be adaptively changed via one or more currently running processes in the field programmable device or by control through one or more graphical user interfaces described below. Alternatively, the laser mirror currents may be automatically adapted based on the gain-voltage maps at different temperatures (also referred to herein as the laser mirror currents adaptation).

In an aspect of the present disclosure, a remote operator may have complete control of parameter settings of the tunable laser, via various graphical user interfaces (GUIs) configured to communicate through embedded processes in the field programmable device 103 or 531 (e.g., FPGA or PLD or the like) to the laser current and temperature settings of the tunable laser. For example, the remote operator may change various parameter settings at different temperature settings and observe optical output spectra. In the example, FIGS. 8A-11B show GUIs that may be configured to control the laser current and temperature settings at 23° C., 30° C. and 40° C., with respective output spectra under the control of an operator via the GUIs.

In one implementation, the GUI function may be integrated in the field programmable device or a system including the field programmable device, connected to the system via one or more wireless techniques, or connected to the system over optical transmission line(s) from a remote site or location. In particular, the GUI control function may be performed at the system via one or more communication interfaces including API, I2C, GPIO, or etc. of an optical transmitter (or transceiver). Also, one or more control signals may be supplied from a GUI of the system, a GUI connected to the system via one or more wireless techniques, or a GUI connected to the system over optical transmission

line(s) where the one or more control signals come from a GUI of another system at a remote site. Further, when the one or more control signals come from the GUI of another system at the remote site, the optical receiver of the system may read or decode input signals directly to control a wavelength of the system. Alternatively, the one or more control signals from the GUI of another system at the remote site may be received and decoded by a host coupled to the system and subsequently issue one or more commands to control the wavelength of the system.

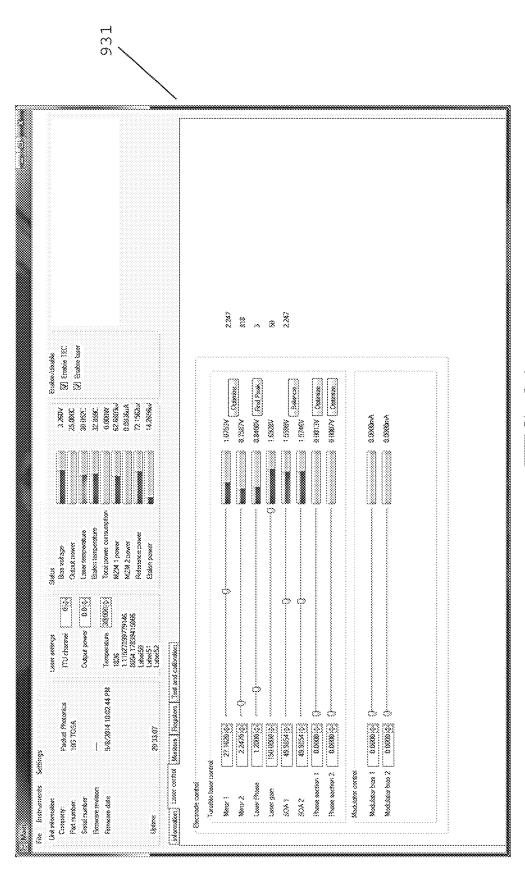

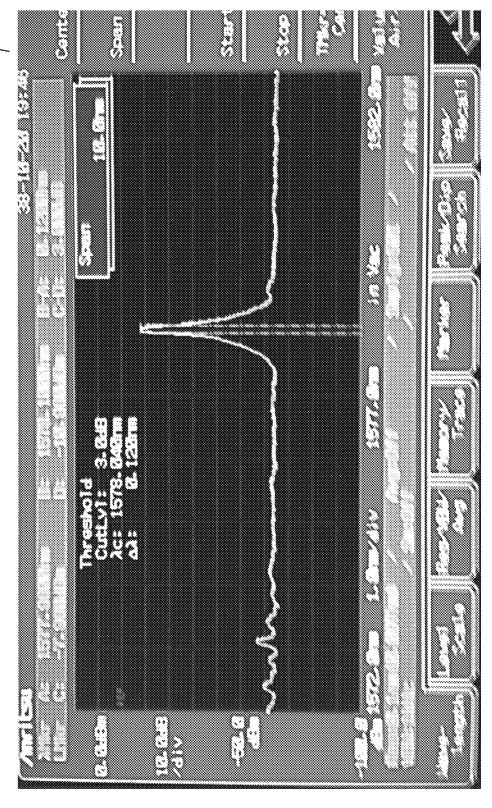

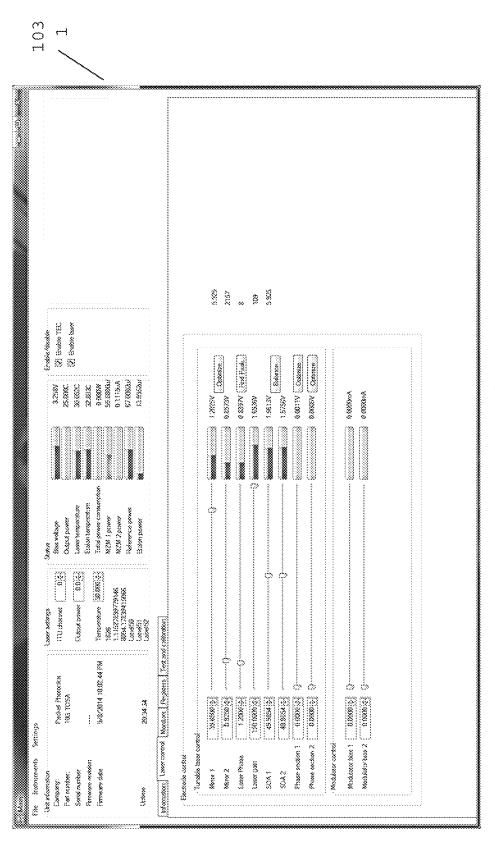

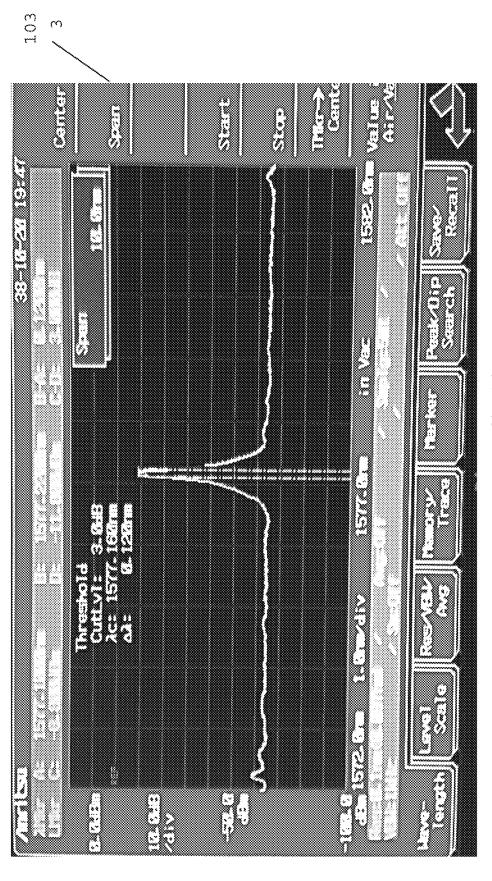

By way of example, FIG. 8A illustrates laser current and temperature settings from GUI control 831 for a temperature value of 23° C. with laser mirror current adaptation enabled, and FIG. 8B shows its corresponding optical spectrum output 833. FIG. 9A illustrates laser current and temperature 15 settings from GUI control 931 for a temperature value of 30° C. without laser mirror current adaptation, and FIG. 9B shows its corresponding optical spectrum output 933. FIG. 10A illustrates laser current and temperature settings from GUI control 1031 for a temperature value of 30° C. with 20 laser mirror current adaptation enabled, and FIG. 10B shows its corresponding optical spectrum output 1033. FIG. 11A illustrates laser current and temperature settings from GUI control 1131 for a temperature value of 40° C. with laser mirror current adaptation enabled, and FIG. 11B shows its 25 corresponding optical spectrum output 1133.

As noted, for the temperature values of 23° C. and 40° C. is shown only with the current correction function enabled, whereas for 30° C. is shown laser current settings and example spectra both with and without the current correction. In the case of 30° C., it is noted that the optical spectrum output is centered at 1577.160 nm with laser mirror current adaptation enabled, while the optical spectrum output is centered at 1578.040 nm without laser mirror current adaptation enabled. As such, the present disclosure may provide the operator at a remote location (e.g., at a host device) with enhanced capability to control various parameter settings of the tunable laser, as well as operational parameters relating to one or more processes concurrently running in the field programmable device, via the one or more GUIs as shown in FIGS. 8A, 9A, 10A, and 11A.

# Linewidth Reduction Algorithm—Digital Signal Processing

In an aspect of the present disclosure, a linewidth reduction algorithm may be digitally implemented as a concurrent, independent module or process in the field programmable device 103 or 531, such as the FPGA, PLD, or the like. By way of example, the linewidth reduction algorithm, such as the Pound-Drever-Hall (PDH) technique is a widely used and powerful approach for stabilizing the frequency of light from tunable lasers by locking to a stable cavity. The range of applications for the PDH technique is broad and may include interferometric gravitational wave detectors, 55 atomic physics, and time measurement standards, many of which also use related techniques such as frequency modulation spectroscopy.

FIG. 12 illustrates a typical implementation of an analog PDH control system. The emitted light from a laser 1201 is 60 split by a splitter 1211 by some ratio and a part is phase modulated using an external clock source 1213. The phase modulated signal is sent through a circulator 1215 and to a Fabry-Perot filter 1217, and the reflected light from the Fabry-Perot filter 1217 is detected by a photodetector 1221 65 and subsequently mixed with an original clock source signal to generate an error signal 1223. The error signal 1223 is

18

then signal processed and used on the laser to rectify phase aberrations, thus reducing its linewidth. As noted, in an aspect of the present disclosure, a PDH feedback loop may be implemented as a concurrent, independent module or process in the field programmable device for high bit rate coherent communications as shown in FIG. 13.

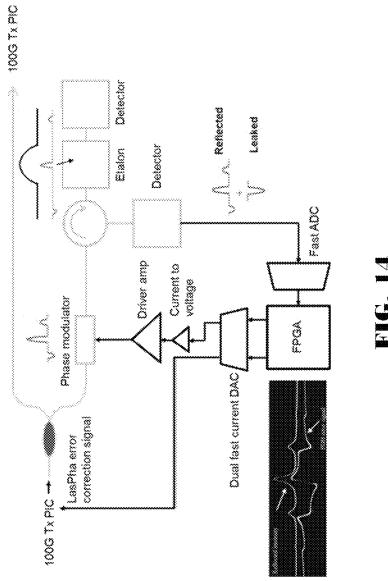

In an aspect of the present disclosure, an example of a system with a 100 Gbps transmitter using a wavelength locker system as an optical detection system is illustrated in FIG. 13. The advantages of the present disclosure for linewidth narrowing or reduction, required for coherent communications and other high bit rate communications (and spectrally efficient communications systems), may include that the control circuitry may be implemented as a concurrent, independent module or process in the field programmable device 103 or 531, such as the FPGA, PLD or the like, running at a clock speed independent of other control loop processes and optimized for a desired linewidth. Additionally, in one implementation, the same optics, optoelectronics, analog electronics and analog-todigital circuits used for other purposes, e.g., a wavelength locker 1323, may also be dual used for the linewidth narrowing, e.g., PHD circuit 1325, thereby reducing the cost, complexity, size, weight and power of a low linewidth transceiver or transmitter, which may be implemented in accordance with an aspect of the present disclosure. Using the present technology described herein, thus, all of the building blocks of the analog PDH control system illustrated in FIG. 12 may be implemented in reprogrammable hardware gates of the field programmable device 103 or 531. An illustration of a PDH linewidth control system that re-uses (dual use) wavelength locker components is shown in FIG. 13 with the PIC, external components and the PDH control loop.

Traditionally, PDH algorithms use analog electronics to form the filtering, demodulation and feedback portions of a noise reduction loop. These functions may be problematic to perform in a microprocessor or a microcontroller, due to certain requirements for fixed low latency in a path from a detector to a laser phase modulator. However, advantages of the present technology may provide that the field programmable device 103 0r 531 enables implementations of digital signal processing (DSP) functions as fixed, dedicated modules or processes, allowing precise control of latency. As such, the implementation of the PDH feedback loop in accordance with the present disclosure may result in immunity from analog noise and electronic magnetic interference (EMI) sources and programmability which greatly simplifies calibration and optimization of feedback loop characteristics and linewidth reduction performance.

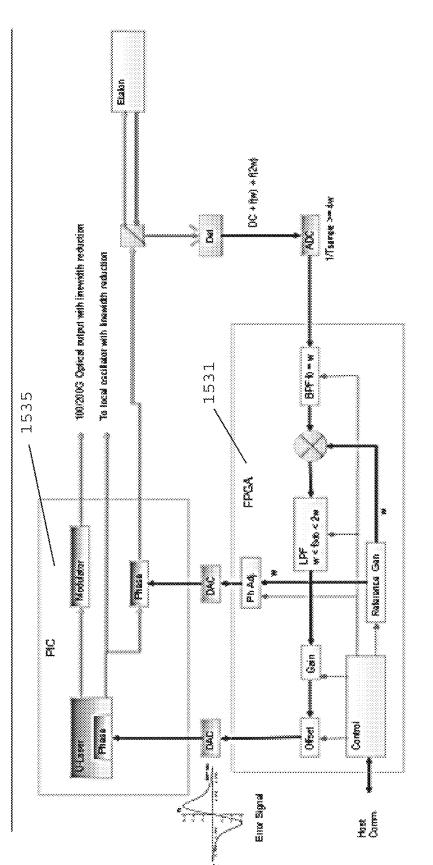

FIG. 14 shows an example block diagram illustrating one embodiment showing connections of a field programmable device (e.g., FPGA or PLD or the like) to ADC, DACs, laser and optical path, in accordance with an aspect of the present disclosure. FIG. 15 shows an example block diagram illustrating implementation of filtering function(s) embedded in a field programmable device for the PDH loop, in accordance with an aspect of the present disclosure. In the example, the detected optical power from a reflected etalon optical path is digitized and fed into the field programmable device such as an FPGA 1531, which is configured to perform the PDH algorithm filtering, demodulation, and produce an error cancellation signal that drives the laser phase modulator in a photonic integrated circuit (PIC) 1535. The FPGA 1531 is also configured to produce a reference

modulation frequency that drives an etalon input optical signal phase modulator through a DAC, as shown in FIG. 15

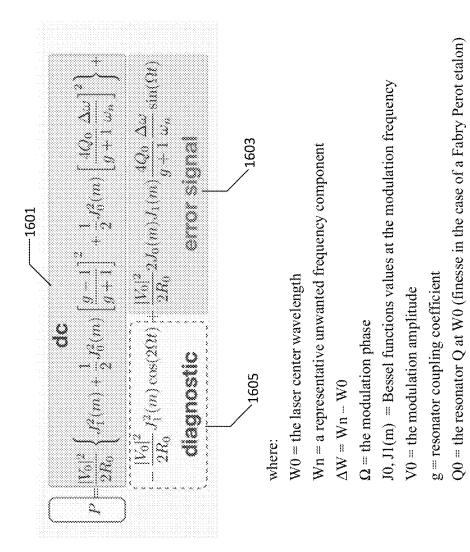

In another aspect of the present disclosure, in the example of FIG. 15, an equation for the detected power from the 5 etalon reflected optical signal, represented as a function of a difference between the reference modulation frequency and a representative unwanted frequency component may be derived and used, as shown in FIG. 16. In the equation, the detected power (P) includes three components, a DC term 10 1601, a component at a modulation frequency (error signal 1603), and a component at twice the modulation frequency (diagnostic 1605). The component at twice (2×) the modulation frequency (diagnostic 1605) may be used for test and calibration of a system. In an example implementation of the 15 PDH algorithm, through modulating a laser wavelength such that side lobes occur on a highly sloped portion of a resonator response, an amplitude of the component at the modulation frequency (error signal 1603) is proportional to a difference between any extraneous frequency components 20 and the modulation frequency, and responds oppositely to positive and negative phase perturbations, thus producing a desired error signal.

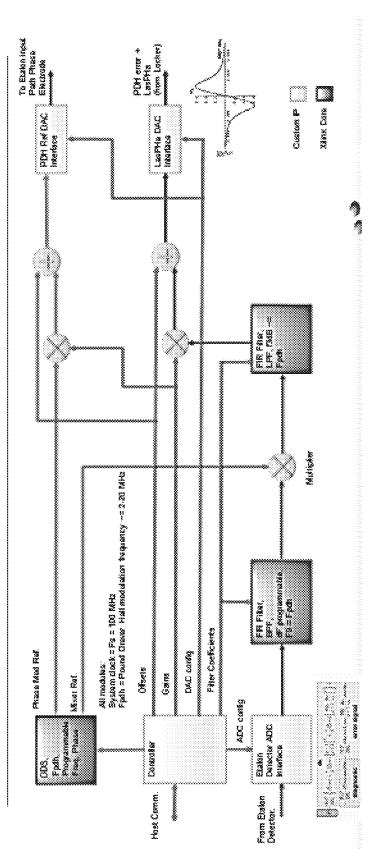

Further, in one implementation of the PDH algorithm, the error signal may be extracted and fed back to the phase 25 modulator in the tunable laser to cancel undesired components as shown in FIG. 17. Here, ADC interface logic receives a digitized power signal from the etalon reflected optical path detector. A digital FIR band pass filter centered at the modulation frequency removes the DC component and 30 2× modulation frequency components from the detected power signal. The band pass output is then multiplied by the modulation frequency reference, which is generated by a DDS. The result is a demodulated error signal with a component at 2x modulation frequency which is unwanted. 35 As a result, a FIR low pass filter with cutoff at about the modulation frequency removes the unwanted 2× modulation frequency component, while leaving any error components up to the modulation frequency.

The resulting error signal goes through gain and offset 40 blocks to provide proper amplitude and DC offset to drive the laser phase modulator, and then goes to the DAC interface logic which formats the data and sends it to the DAC. The design latency in the example path shown between the detected power from the etalon and the laser 45 phase electrode, including the external ADC and DAC is less than 500 ns, the main contribution being from the FIR filters. Optimization of the foregoing algorithm may result in even lower latency. The reference DDS provides phase adjustment of the modulator reference signals sent to both the 50 demodulator and the reference phase modulator such that the response can be nulled for initial calibration. Gain and offset adjustment are also provided for the reference modulation output. FIR filter coefficients, reference frequency and phase, gains, and offsets are all programmable by the host, 55 enabling ease of algorithm optimization, tuning and calibration of the tunable laser and it associated systems. As such, in an aspect of the present disclosure, the linewidth reduction algorithm may be digitally implemented as a concurrent, independent module or process in the field program- 60 mable device 103 or 531, such as the FPGA, PLD, or the like.

# Real-time Monitoring of Parameters

Many parameters in a tunable laser/modulator require real time monitoring and feedback to dynamic control loops. 20

Parameters also require measurement at many operating points for calibration and analysis purposes, and the speed with which these measurements can be performed may be critical to enabling large scale production of tunable lasers.

In an aspect of the present disclosure, the present technology enables such large scale production of tunable lasers. In other words, parallel architectures that may be created using field programmable devices, such as FPGAs or PLDs or the like, enable monitoring of the critical parameters and feed them back to multiple control loops simultaneously with minimal latency, whereas a microprocessor or microcontroller would have to process and distribute all of the information in a serial and/or sequential manner.